CY7C1041 BV33-12ZC - [ CYPCY7C1041 BV33-12ZC (A3) ]

Digital IC Shop

CY7C1041 BV33-12ZC - [ CYPCY7C1041 BV33-12ZC (A3) ]

750Ft

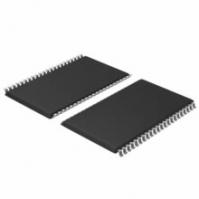

256K x 16 Static RAM

CY7C1041BV33

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-05168 Rev. ** Revised November 15, 2001

041BV33

Features

• High speed

— tAA = 12 ns

• Low active power

— 612 mW (max.)

• Low CMOS standby power (Commercial L version)

— 1.8 mW (max.)

• 2.0V Data Retention (600 µW at 2.0V retention)

• Automatic power-down when deselected

• TTL-compatible inputs and outputs

• Easy memory expansion with CE and OE features

Functional Description

The CY7C1041BV33 is a high-performance CMOS Static

RAM organized as 262,144 words by 16 bits.

Writing to the device is accomplished by taking Chip Enable

(CE) and Write Enable (WE) inputs LOW. If Byte Low Enable

(BLE) is LOW, then data from I/O pins (I/O0 through I/O7), is

written into the location specified on the address pins (A0

through A17). If Byte High Enable (BHE) is LOW, then data

from I/O pins (I/O8 through I/O15) is written into the location

specified on the address pins (A0 through A17).

Reading from the device is accomplished by taking Chip

Enable (CE) and Output Enable (OE) LOW while forcing the

Write Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW,

then data from the memory location specified by the address

pins will appear on I/O0 to I/O7. If Byte High Enable (BHE) is

LOW, then data from memory will appear on I/O8 to I/O15. See

the truth table at the back of this data sheet for a complete

description of read and write modes.

The input/output pins (I/O0 through I/O15) are placed in a

high-impedance state when the device is deselected (CE

HIGH), the outputs are disabled (OE HIGH), the BHE and BLE

are disabled (BHE, BLE HIGH), or during a write operation (CE

LOW, and WE LOW).

The CY7C1041BV33 is available in a standard 44-pin

400-mil-wide body width SOJ and 44-pin TSOP II package

with center power and ground (revolutionary) pinout.

Buy Now : https://www.digitalicshop.com/product_info.php?products_id=&language=en

256K x 16 Static RAM

CY7C1041BV33

Cypress Semiconductor Corporation • 3901 North First Street • San Jose • CA 95134 • 408-943-2600

Document #: 38-05168 Rev. ** Revised November 15, 2001

041BV33

Features

• High speed

— tAA = 12 ns

• Low active power

— 612 mW (max.)

• Low CMOS standby power (Commercial L version)

— 1.8 mW (max.)

• 2.0V Data Retention (600 µW at 2.0V retention)

• Automatic power-down when deselected

• TTL-compatible inputs and outputs

• Easy memory expansion with CE and OE features

Functional Description

The CY7C1041BV33 is a high-performance CMOS Static

RAM organized as 262,144 words by 16 bits.

Writing to the device is accomplished by taking Chip Enable

(CE) and Write Enable (WE) inputs LOW. If Byte Low Enable

(BLE) is LOW, then data from I/O pins (I/O0 through I/O7), is

written into the location specified on the address pins (A0

through A17). If Byte High Enable (BHE) is LOW, then data

from I/O pins (I/O8 through I/O15) is written into the location

specified on the address pins (A0 through A17).

Reading from the device is accomplished by taking Chip

Enable (CE) and Output Enable (OE) LOW while forcing the

Write Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW,

then data from the memory location specified by the address

pins will appear on I/O0 to I/O7. If Byte High Enable (BHE) is

LOW, then data from memory will appear on I/O8 to I/O15. See

the truth table at the back of this data sheet for a complete

description of read and write modes.

The input/output pins (I/O0 through I/O15) are placed in a

high-impedance state when the device is deselected (CE

HIGH), the outputs are disabled (OE HIGH), the BHE and BLE

are disabled (BHE, BLE HIGH), or during a write operation (CE

LOW, and WE LOW).

The CY7C1041BV33 is available in a standard 44-pin

400-mil-wide body width SOJ and 44-pin TSOP II package

with center power and ground (revolutionary) pinout.